HOME >연구내용 >핵심과제1

HOME >연구내용 >핵심과제1

2-3. 고성능 소프트 집적회로 기술 개발

| 연구참여자

|

|

||||||||||||||||||||||||

| 연구목표

기존의 유기 재료 기반의 소프트 소자로 구현이 불가능한 고성능 소프트 소자 개발을 위해 단결정 실리콘을 이용한 고성능 유연 소자를 개발하고, strain을 최소화 하는 구조를 연구하여 높은 유연성을 갖는 고성능 실리콘 소자 및 회로 기술 개발

| 연구내용

Topic 1. 유연 실리콘 소자를 위한 전사 공정 개발 및 유연 특성 분석

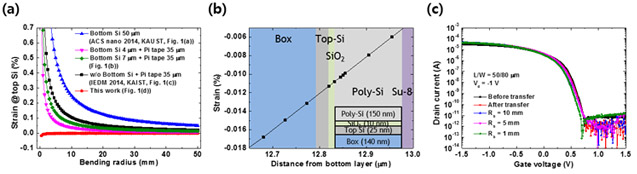

- 단결정 실리콘 멤브레인 제작 공정 개발 및 strain 분석

- SOI (silicon on insulator) 웨이퍼의 bottom silicon을 에칭하고 남은 수백 나노 두께의 얇은 멤브레인을 플라스틱 기판에 전사하는 공정 개발

- 전사된 실리콘 멤브레인의 유연 특성을 분석하기 위해 굽힘 정도에 따른 strain을 전기적으로 분석하고 시뮬레이션을 통해 검증.

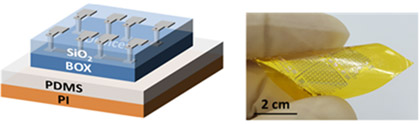

PDMS/PI 필름에 전사된 실리콘 멤브레인 구조 및 샘플 사진

Topic 2. Rb<=1mm의 고유연 FDSOI 고성능 트랜지스터 개발

(a) 기존 구조들에 비해 neutral mechanical plane의 최적화를 통해 향상된 strain-free 구조 (b) 제안된 구조의 strain simulation (c) 1 mm bending 시 성능 열화 없는 소자 특성

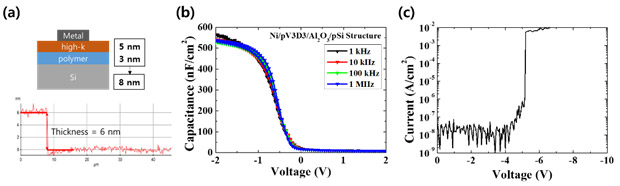

Topic 3. iCVD를 이용한 소프트 소자용 게이트 절연막 형성 및 분석

(a) 단결정 실리콘 위에 형성된 High-k/polymer 이중층 구조와 AFM으로 측정한 실제 두께 (b) Capacitance-Voltage 특성 (c) Current-Voltage 특성

| 기대효과

| 대표연구실적